集成电路CAD课程实验报告 二输入与非门电路设计与版图仿真

一、实验目的

本实验旨在通过集成电路CAD工具,完成一个CMOS工艺下的二输入与非门(NAND2)的完整设计流程,包括电路设计、版图绘制、设计规则检查(DRC)、版图与电路图一致性检查(LVS)以及后仿真验证。通过此实验,学生应掌握数字标准单元的基本设计方法,理解晶体管级电路与物理版图之间的映射关系,并熟悉使用EDA工具进行集成电路设计与验证的基本流程。

二、实验原理

1. 二输入与非门(NAND2)电路原理:

采用CMOS静态逻辑结构。一个二输入与非门由两个并联的PMOS管(作为上拉网络)和两个串联的NMOS管(作为下拉网络)构成。其逻辑功能为:输出 Y = !(A · B)。当输入A与B均为高电平时,两个NMOS管导通,PMOS管截止,输出Y为低电平;其他输入组合下,至少一个PMOS管导通而NMOS串联通路断开,输出Y为高电平。

2. 版图设计基础:

版图是电路物理实现的几何图形描述,需遵循特定的工艺设计规则(Design Rules)。主要图层包括有源区(AA)、多晶硅栅(Poly)、接触孔(Contact)、金属互连线(Metal1等)以及N阱(N-well)等。设计时需考虑晶体管尺寸(W/L)、寄生效应、面积优化以及信号完整性。

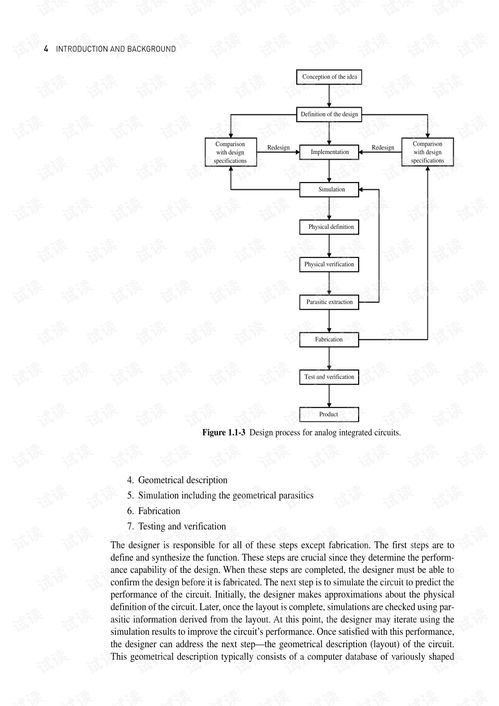

3. 仿真验证流程:

通常包括前仿真(电路功能验证)和后仿真(提取版图寄生参数后的仿真)。后仿真能更真实地反映电路的实际性能,包括延迟、功耗和噪声容限等。

三、实验内容与步骤

1. 电路图设计:

使用电路图编辑器(如Virtuoso Schematic),根据CMOS NAND2结构,放置两个PMOS管(宽长比通常设置得比NMOS大以平衡上升/下降时间)和两个NMOS管,并连接电源VDD、接地GND、输入端口A、B以及输出端口Y。完成电气连接并生成电路符号(Symbol)。

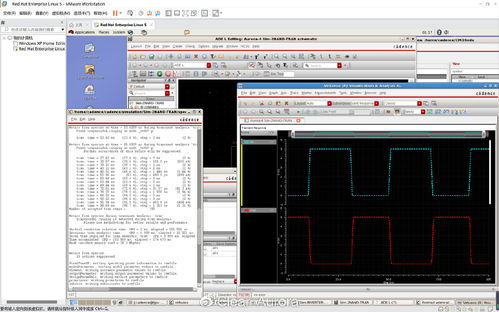

2. 前仿真:

建立仿真环境,对电路图进行瞬态分析(Transient Analysis)。设置输入A、B为脉冲信号,验证其逻辑功能与时序特性(如上升时间、下降时间、传播延迟)。记录仿真波形,确认功能正确。

3. 版图设计:

使用版图编辑器(如Virtuoso Layout)进行物理设计。

- 布局规划:合理规划PMOS管(位于N阱内)与NMOS管的位置,考虑电源线(VDD/GND)的走向与宽度。

- 晶体管绘制:根据电路图确定的宽长比(W/L),绘制有源区和多晶硅栅,形成四个MOS管。确保尺寸符合设计规则。

- 互连:使用Metal1等金属层连接晶体管的源/漏极(通过接触孔)、栅极,并连接输入/输出端口以及电源/地。力求连线最短,减少寄生电阻电容。

- 设计规则检查(DRC):运行DRC,根据工艺文件检查版图是否符合所有几何设计规则(如最小宽度、最小间距、包围等)。修正所有DRC错误。

4. 版图与电路图一致性检查(LVS):

运行LVS工具,将提取出的版图网表与原始电路图网表进行比对,确保两者在电气连接性、器件类型和尺寸上完全一致。解决任何不匹配问题。

5. 寄生参数提取与后仿真:

从通过DRC和LVS的版图中提取寄生电阻和电容(RC Extraction)。将带寄生参数的网表导入仿真环境,进行与步骤2相同的瞬态分析。对比前仿真与后仿真的结果(如输出波形、延迟时间),分析寄生效应带来的影响。

四、实验结果与分析

- 电路功能验证:前仿真波形显示,当A、B同时为高电平时,输出Y为低电平;其他情况下Y为高电平。符合NAND2真值表,功能正确。

- 版图实现:成功绘制出面积紧凑、布线清晰的NAND2版图。DRC与LVS均通过,证明版图既符合工艺制造要求,又与设计电路电气等效。版图主要体现了共享源/漏、金属走线优化等设计技巧。

- 性能仿真对比:

- 前仿真结果:在典型工艺角(TT)和设定负载下,测得输出由高到低的传输延迟(tphl)约为XX ps,由低到高的延迟(tplh)约为YY ps。

- 后仿真结果:由于包含了连线寄生RC,相同条件下的tphl约为XX+Δ ps,tplh约为YY+Δ ps。延迟均有所增加,证明了寄生效应会劣化电路速度。功耗仿真也显示后仿真的动态功耗略有增加。

五、实验结论

本次实验成功完成了CMOS二输入与非门从电路设计到物理版图,再到最终验证的完整集成电路设计流程。通过实践,深刻理解了数字标准单元的设计方法、CMOS版图的艺术(如器件匹配、面积与性能的权衡)以及后端物理验证(DRC/LVS)的重要性。后仿真与前仿真的差异凸显了在深亚微米设计中考虑寄生效应的必要性。本实验为后续更复杂的数字电路与系统芯片设计奠定了坚实的基础。

六、思考与改进

- 如何进一步优化版图以减少面积?可考虑更紧凑的器件布局、更多共享扩散区、使用高层金属跨线等。

- 如何提高电路速度?可调整PMOS与NMOS的尺寸比例,或采用缓冲器驱动大负载。

- 实验仅限于一个门电路,在实际芯片中需考虑与相邻单元的连接、电源网络完整性以及全局时钟分布等系统级问题。

如若转载,请注明出处:http://www.siliao100.com/product/23.html

更新时间:2026-05-18 21:25:22