芯片设计之CDC异步电路分析(五)——集成电路设计中的同步策略与实现

在集成电路设计中,跨时钟域(CDC,Cross-Domain Clock)问题一直是确保系统稳定性和数据完整性的关键挑战。随着芯片规模的扩大和时钟域的增多,异步电路的设计与分析显得尤为重要。本文将重点探讨在集成电路设计层面,如何系统性地解决CDC问题,涵盖常见同步策略、设计方法与实现要点。

一、CDC问题的本质与影响

在复杂SoC(系统级芯片)中,不同功能模块可能工作在不同的时钟频率下,甚至采用完全异步的时钟源。当时钟域之间存在数据交互时,便会引发CDC问题。若不妥善处理,将导致亚稳态(Metastability)、数据丢失或逻辑错误,严重影响芯片功能。因此,在集成电路设计的早期阶段,就必须将CDC分析与同步机制纳入整体架构规划。

二、集成电路设计中的同步策略

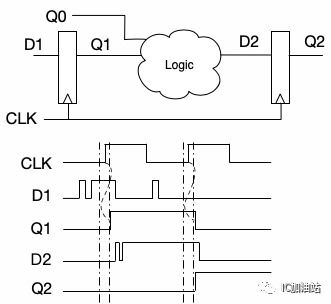

- 同步器设计:这是处理CDC最基本的方法,通常使用两级或多级触发器链来降低亚稳态传播风险。在电路设计中,需根据时钟频率、时序余量等因素选择合适的同步器级数,并在布局布线时确保其物理位置靠近目标时钟域,以减少延迟偏差。

- 握手协议:适用于数据带宽要求不高但需确保数据准确传输的场景。通过请求(Request)和应答(Acknowledge)信号实现跨时钟域的数据交换,虽增加了一定的延迟和设计复杂度,但能有效避免数据冲突。在集成电路设计中,握手逻辑需仔细验证以避免死锁或活锁。

- 异步FIFO:这是处理大数据量跨时钟域传输的经典方案。通过双端口RAM和读写指针同步机制,实现数据的缓冲与安全传递。在设计时,需重点关注指针编码(如格雷码)以减少亚稳态风险,并合理规划FIFO深度以平衡面积和性能。

- 时钟门控与电源管理:在现代低功耗芯片中,时钟域可能动态开关,这进一步加剧了CDC的复杂性。设计时需考虑电源状态转换期间的信号稳定性,并采用隔离单元(Isolation Cell)和电平转换器(Level Shifter)等特殊单元来确保信号完整性。

三、设计实现与验证要点

- RTL设计规范:在寄存器传输级(RTL)编码阶段,应明确标注时钟域边界,并采用模块化的同步接口设计。例如,为每个跨时钟域信号设计专用的同步模块,避免在业务逻辑中混杂CDC处理代码。

- 静态时序分析(STA)与CDC专项检查:除了传统时序收敛,必须使用EDA工具进行CDC验证,检测未同步信号、复位冲突、时钟耦合等问题。工具如Synopsys的SpyGlass CDC或Cadence的JasperGold可帮助识别设计漏洞。

- 物理设计考量:在布局布线阶段,同步器应放置于相关时钟域内,并尽量缩短时钟网络延迟差。需注意信号线跨电压域时的电平一致性,避免因电压差异导致逻辑误判。

- 系统级验证:通过仿真和FPGA原型验证,模拟真实场景下的时钟抖动、频率变化等条件,测试CDC机制在极端情况下的鲁棒性。形式验证也可用于证明同步协议的正确性。

四、未来趋势与挑战

随着工艺节点演进和异构计算兴起,芯片内时钟域数量激增,且异步接口(如Die-to-Die互连)日益普遍。未来CDC设计将更注重自动化同步插入、机器学习辅助的时序优化,以及针对3D-IC等新架构的跨堆叠同步方案。设计人员需持续更新方法论,结合工具与经验,在性能、面积和可靠性间取得最佳平衡。

CDC异步电路分析是集成电路设计中不可或缺的一环。只有从架构、设计到验证全流程贯彻严谨的同步策略,才能构建出稳定可靠的高性能芯片,迎接日益复杂的应用挑战。

如若转载,请注明出处:http://www.siliao100.com/product/1.html

更新时间:2026-04-22 21:25:27