不止光刻机 挡在国产集成电路设计路上的“三座大山”

提及国产芯片的发展瓶颈,公众的视线往往聚焦于光刻机等尖端制造设备。诚然,这是我们必须攻克的关键壁垒,但绝非唯一障碍。在芯片诞生的起点——集成电路设计领域,同样横亘着三座必须翻越的“大山”,它们共同制约着我国芯片产业自主创新能力的跃升。

第一座大山:高端核心IP(知识产权核)与EDA工具的依赖之困。

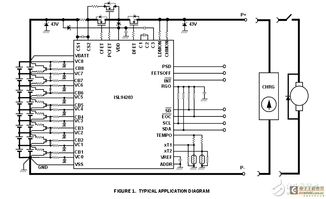

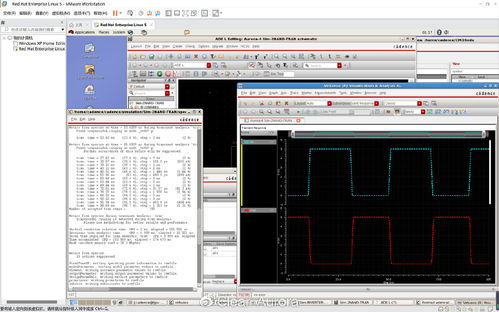

芯片设计如同建造摩天大楼,EDA(电子设计自动化)工具就是建筑师的全套绘图与仿真软件,而各类经过验证的IP核(如CPU、GPU、高速接口等核心模块)则是预制好的核心构件。目前,全球EDA市场与高端IP市场由少数几家海外巨头高度垄断。国内设计企业,即便是龙头企业,在设计最先进工艺节点的复杂芯片时,也严重依赖这些“外脑”和“外购模块”。这不仅带来高昂的授权成本,更在供应链安全、设计迭代效率、以及最终产品性能的自主优化上埋下隐患。缺乏自主可控、全流程且能支撑先进工艺的EDA工具链和经过大规模量产验证的高端IP库,是我国集成电路设计向上突破的首要瓶颈。

第二座大山:顶尖复合型设计人才的稀缺之困。

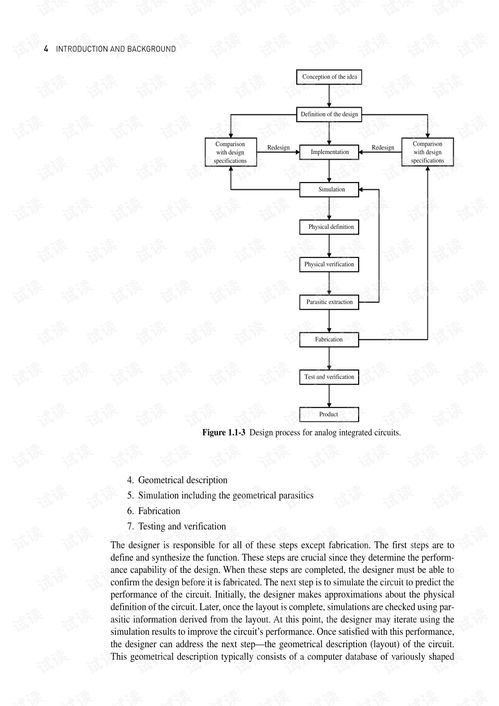

芯片设计是知识、经验与创造力高度密集的领域。一颗先进芯片的架构规划、前端设计、后端物理实现、验证测试,需要跨学科、懂架构、通工艺、有经验的顶尖工程师团队通力协作。我国芯片行业人才缺口巨大,尤其缺乏两类关键人才:一是能定义世界级芯片产品、具有系统视野和前瞻思维的架构师;二是精通先进工艺物理特性、能解决纳米级设计挑战的全流程工程师。人才培养周期长、行业积累要求高,加之国际竞争激烈导致的人才争夺,使得人才短缺问题在追求快速突破的背景下显得尤为突出,成为制约设计水平提升的核心软肋。

第三座大山:设计与制造协同脱节的生态之困。

芯片是设计与制造深度耦合的产物。国际领先的设计公司(如高通、苹果)与顶尖代工厂(如台积电、三星)之间存在着基于长期合作和信任的紧密协同。设计团队需要代工厂提供精确的工艺设计套件(PDK)和丰富的技术参考流程,并在设计早期就进行可制造性设计(DFM)的深度优化。目前,国内最先进的制造工艺与国际最前沿尚有代差,导致国内设计公司在开发顶级性能产品时,往往仍需寻求海外代工。而国内设计与制造环节的互动、迭代和共同优化机制尚不成熟,未能形成类似“苹果-台积电”或“英伟达-台积电”那样强强联合、相互驱动的紧密产业生态。这种设计与制造的脱节,使得国内设计成果难以在最先进的制造平台上得到最佳淬炼和快速迭代。

突破集成电路设计领域的瓶颈,是一场需要多方协同、持之以恒的系统工程。它要求我们不仅要持续投入研发,攻克EDA与核心IP的技术壁垒;更要构建良好的人才培养与吸引体系,夯实智力基础;必须着力推动国内设计、制造、封装测试等产业链各环节的深度融合,构建健康、自主、充满活力的芯片产业生态。只有翻越这“三座大山”,国产芯片才能真正在创新的源头——设计端,掌握自主权与竞争力,为最终跨越整个芯片产业的“珠穆朗玛峰”奠定坚实基础。

如若转载,请注明出处:http://www.siliao100.com/product/21.html

更新时间:2026-05-06 20:25:43