测微仪激励信号发生电路设计与集成电路实现

测微仪作为一种高精度测量仪器,其核心性能很大程度上依赖于稳定、精确的激励信号。激励信号发生电路负责产生驱动传感器(如电感式、电容式传感器)所需的高频交变信号,其质量直接决定了测微仪的灵敏度、分辨率和稳定性。本文将探讨测微仪激励信号发生电路的关键设计要素,并阐述其向专用集成电路(ASIC)集成的设计思路与优势。

一、激励信号发生电路的核心要求与设计

- 信号质量要求:

- 频率稳定性:激励信号的频率必须高度稳定,通常需要达到10^-5量级或更高,以避免因频率漂移引入测量误差。这要求核心振荡器具有低温度系数和低相位噪声。

- 幅度稳定性:信号幅度直接影响传感器的灵敏度,需要设计精密的自动增益控制(AGC)电路或采用幅度反馈机制,以维持输出幅度的恒定,通常要求优于0.1%。

- 波形纯度:理想情况下应为纯净的正弦波。谐波失真和噪声会干扰传感器的响应和解调过程,因此需要设计有效的滤波和整形电路,确保总谐波失真(THD)足够低。

- 经典电路架构:

- 文氏桥振荡器:是经典的正弦波发生器方案,通过RC选频网络和同相放大器构成正反馈环路产生振荡。其优点是电路简单、波形好。关键设计点在于采用热敏电阻等非线性元件或AGC电路来实现稳定的幅度控制。

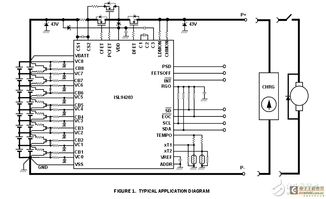

- 锁相环(PLL)合成:对于需要更高频率稳定性或可编程频率的应用,可采用基于晶体振荡器参考的PLL频率合成方案。通过编程锁相环的分频比,可以灵活产生所需频率,且频率稳定度直接继承自高稳晶振。

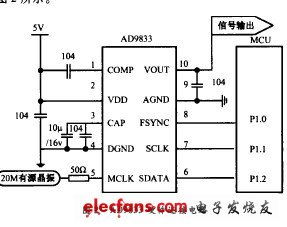

- 直接数字合成(DDS):DDS技术通过数字方式生成波形,具有极高的频率分辨率和快速变频能力。结合高性能数模转换器(DAC)和低通滤波器,可以产生非常纯净且参数可灵活配置的激励信号,是高性能测微仪的发展方向。

- 输出驱动与隔离:生成的激励信号通常需要经过缓冲放大以驱动传感器负载。设计低输出阻抗、高线性度的驱动级至关重要。需考虑电路地与传感器地之间的隔离,采用差分驱动或变压器耦合等方式,以抑制共模干扰。

二、激励信号发生电路的集成电路设计

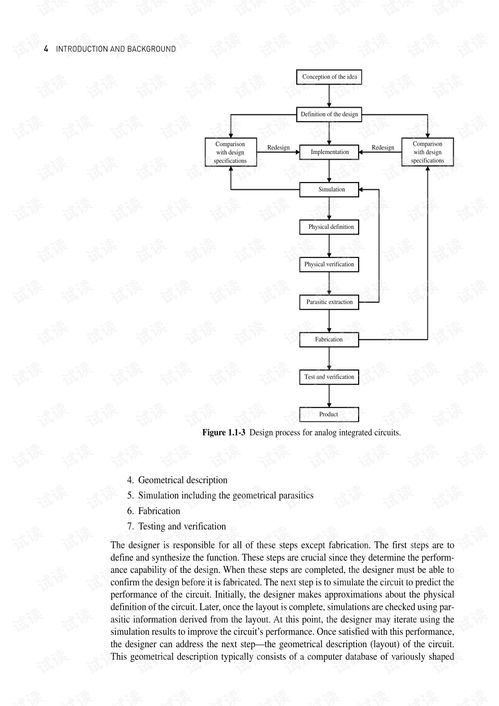

将上述分立电路集成到单片ASIC中,能显著提升测微仪的整体性能、可靠性和集成度。

- 设计目标与优势:

- 微型化与低功耗:将所有模拟功能块集成于单一芯片,极大减小了PCB面积,降低了整体功耗,便于便携式设备开发。

- 性能一致性与稳定性:集成电路的元件匹配性好,受环境寄生效应影响小,能保证批量产品性能的高度一致性和长期稳定性。

- 抗干扰能力强:片上信号路径短,减少了外部电磁干扰(EMI)的引入点。

- 成本效益:在大批量生产时,ASIC方案能有效降低系统物料成本(BOM)和装配成本。

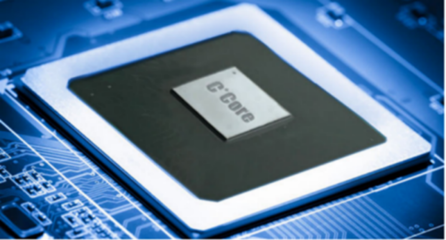

- 关键模块的IC实现:

- 核心振荡器:可采用片上LC振荡器或基于晶体(需外接晶振)的振荡器。为追求高稳定性,设计低噪声、低温度系数的偏置电路和增益控制环是关键。全集成RC振荡器虽然节省空间,但其绝对精度和温漂通常较差,需通过出厂校准或数字修调技术补偿。

- 可编程增益放大器(PGA)与AGC:在模拟域或数字域实现精密的幅度控制。集成高精度电阻网络或乘法型DAC(如MDAC)用于增益调节,配合峰值检测电路构成闭环AGC系统。

- 滤波与波形整形:集成连续时间滤波器(如Gm-C滤波器、有源RC滤波器)对振荡器输出或DAC输出进行低通滤波,以滤除高频杂散和谐波。需要精细设计以平衡滤波性能、芯片面积和功耗。

- 输出驱动级:设计轨到轨、高输出电流能力的运算放大器作为输出缓冲器,并考虑短路保护功能。

- 数字控制接口:现代ASIC通常集成I2C、SPI等数字接口,用于接收来自主控MCU的频率、幅度、波形选择等控制指令,实现智能化配置。若采用DDS方案,则需集成波形查找表(LUT)、相位累加器、DAC等数字/混合信号模块。

- 设计挑战与考量:

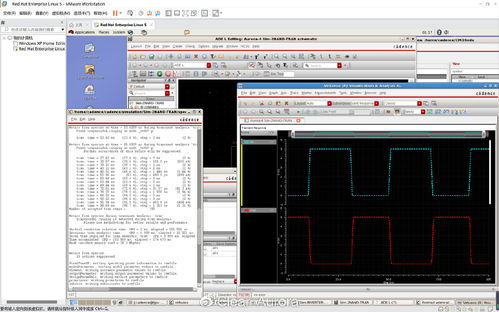

- 混合信号设计:电路同时包含高精度模拟模块和数字控制逻辑,需精心规划电源域、地平面和布局布线,防止数字开关噪声耦合到敏感的模拟信号路径中(如衬底噪声耦合、电源噪声)。

- 工艺选择:需根据性能(如模拟精度、工作频率)和成本选择适宜的半导体工艺(如CMOS、BiCMOS)。

- 测试与校准:集成后,芯片的测试覆盖率和出厂校准策略(如激光修调或电学修调)对保证良率和性能至关重要。

三、

测微仪激励信号发生电路的设计是一个兼顾频率稳定、幅度恒定和波形纯净的系统工程。从经典的分立文氏桥振荡器到灵活的DDS方案,技术不断演进。而将其集成化为专用集成电路,是提升测微仪核心竞争力——精度、可靠性与小型化的必然途径。成功的IC设计需要深入理解传感器激励的模拟前端需求,并娴熟运用混合信号设计技术,在性能、功耗、面积和成本之间取得最佳平衡。随着集成电路工艺的进步和设计工具的完善,功能更强大、集成度更高的测微仪专用信号链SoC(片上系统)将成为未来主流。

如若转载,请注明出处:http://www.siliao100.com/product/15.html

更新时间:2026-04-22 17:24:04