从蓝图到晶体 揭秘集成电路设计与制造的精密之旅

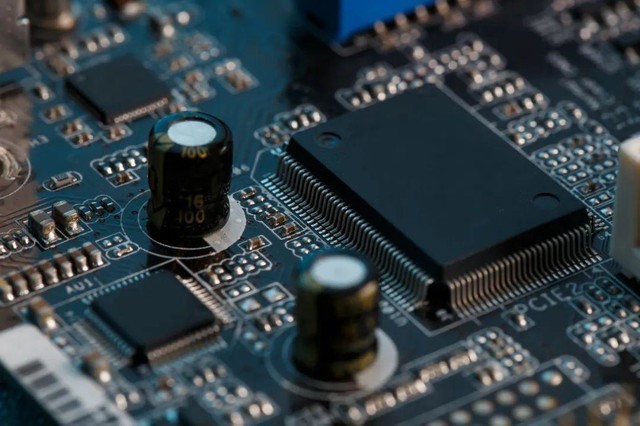

集成电路,作为现代电子设备的心脏,其设计与制造是人类工程智慧的巅峰体现。这一过程融合了物理学、材料科学、计算机工程和精密机械的尖端技术,如同一场在纳米尺度上的宏伟交响。

第一阶段:集成电路设计——在虚拟世界绘制微观蓝图

集成电路的诞生始于设计阶段,这是一个纯粹的数字与创意过程。设计师们并非直接雕刻硅片,而是首先在计算机上构建出复杂的电路模型。

- 系统架构与功能定义:根据芯片的最终用途(如CPU、内存、传感器等),确定其核心功能、性能指标和功耗预算。这如同为一座城市规划功能区。

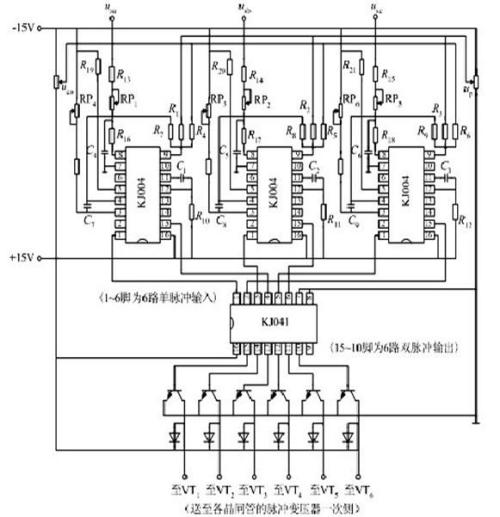

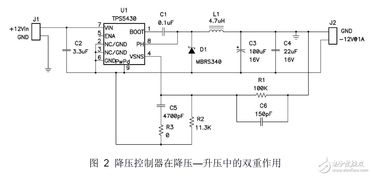

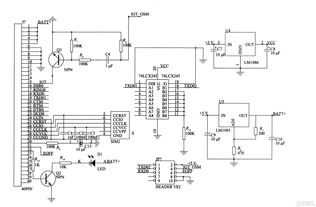

- 逻辑设计与电路设计:工程师使用硬件描述语言(如Verilog或VHDL)将功能转化为具体的逻辑门电路(与门、或门、非门等)及其连接关系。这一步生成了电路的“逻辑原理图”。

- 物理设计(布局布线):这是设计中最关键且复杂的一步。工具软件将逻辑电路转换成实际的物理结构,决定数十亿个晶体管、电阻、电容在硅片上的具体位置,并像规划超微缩高速公路网一样,用金属导线将它们精确连接起来。整个过程必须严格遵守制造工艺的物理极限(如最小线宽,即“工艺节点”,如7纳米、5纳米)。

- 验证与仿真:在投入昂贵制造之前,设计需要通过严格的电气规则检查、时序验证和功能仿真,确保其在理论上万无一失。任何微小的错误都可能导致整个晶圆报废。

最终输出的,是一套名为“光掩模”的电子蓝图,它是一系列包含芯片每一层图案的精密玻璃底板,是连接设计与制造的桥梁。

第二阶段:集成电路制造——在真实世界执行纳米雕刻

制造是将设计蓝图物理复刻到硅片上的过程,其核心是“光刻”技术,在极纯净的环境(超净间)中进行,主要步骤包括:

- 硅片制备:从高纯度单晶硅柱上切割出薄如纸片的硅圆盘(晶圆),并抛光至原子级平整。

- 氧化与沉积:在硅片表面生长或沉积一层层绝缘体(如二氧化硅)和导体(如多晶硅、金属)薄膜,为构建晶体管和导线准备材料。

- 光刻——图案转印的核心:

- 涂胶:在晶圆表面均匀涂覆一层对特定波长光线敏感的光刻胶。

- 曝光:使用紫外光或极紫外光(EUV)等光源,透过前述设计阶段制作的光掩模,将上面的电路图案投影到光刻胶上。掩模版上的不透光区域会阻挡光线,从而在光刻胶上形成潜影。这好比用“光”的笔,在硅片上“临摹”设计蓝图。

- 显影:用化学溶剂洗掉被曝光(或未曝光,取决于光刻胶类型)的部分,使硅片表面的图案显现出来。

- 刻蚀与离子注入:

- 刻蚀:以显影后的光刻胶为保护膜,用物理或化学方法去除未被保护的薄膜材料,从而将光刻胶上的二维图案永久地转移到硅片的薄膜层上。

- 离子注入:向硅片特定区域注入杂质离子,以改变其电学性质,形成晶体管所需的P区和N区。

- 重复与堆叠:制造一个现代芯片需要数十层结构。上述从沉积到光刻、刻蚀的过程需要重复几十次,层层叠加,最终构建起复杂的三维立体电路。

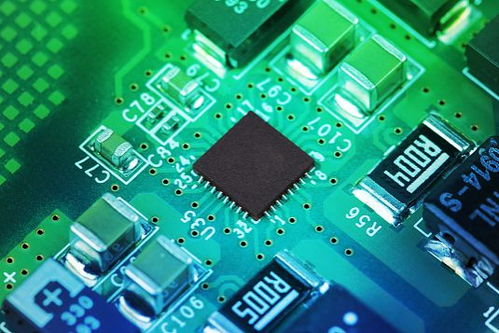

- 封装与测试:制造完成的晶圆被切割成一个个独立的芯片(Die),经过测试后,将其固定在基板上,用细金属线或凸块连接引脚,最后用陶瓷或塑料封装保护起来,成为我们看到的黑色小块。

设计与制造的共舞

集成电路的精密性,源于设计与制造之间天衣无缝的协作。设计定义了功能的极限与智慧的复杂度,而制造则挑战着材料、工艺和精密工程的物理极限。从软件中的一行行代码,到指尖方寸间汇聚的数十亿个晶体管,这场从虚拟到现实的转化,堪称当代最伟大的制造奇迹,持续推动着整个信息时代的向前发展。

如若转载,请注明出处:http://www.siliao100.com/product/4.html

更新时间:2026-04-22 16:18:52